W7500

高性能工业级物联网MCU, Cortex-M0内核+全硬件 TCP/IP 协议栈 + MAC架构, 8路硬件sockets, 128K Flash, 48K SRAM, 3 UART, 2 SPI, 2 I2C

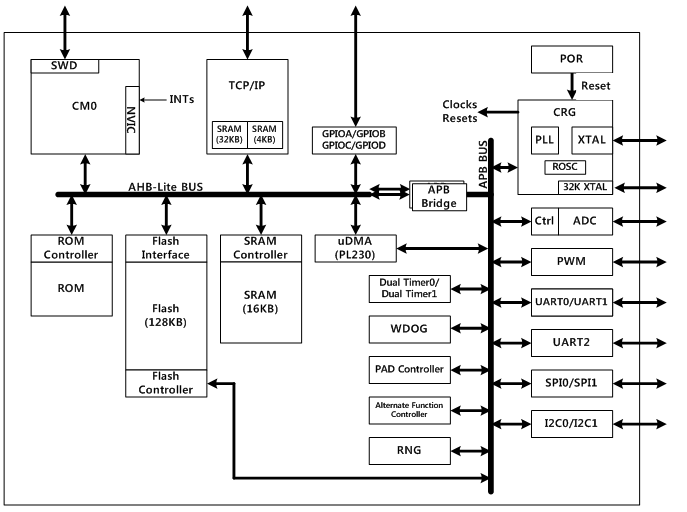

W7500 是一款单芯片的网络卸载处理器(IOP),采用ARM Cortex-M0 内核+全硬件 TCP/IP 协议栈+MAC架构,支持8路硬件socket,满足物联网的需求。其内部集成的以太全硬件 TCP/IP 协议栈,支持 TCP, UDP, IPv4, ICMP, ARP, IGMP 以及 PPPoE 协议,久经市场考验,并得到广泛认可。

特点

ARM Cortex-M0

- 最大时钟频率 48MHz

全硬件TCP/IP核

- 8个socket

- 每个socket拥有最大32KBSRAM

- MII(介质无关接口)

内存

- Flash:128KB

- SRAM:16KB到48KB(如32KB socket 缓存已用,最小可用16KB,如果socket缓存未用,最大可用48KB)

- 用于Boot程序存储的ROM:6KB

时钟,复位及供给管理

- POR(上电复位)

- 稳压器:3.3V到1.5V

- 8到24MHz的外部晶体振荡器

- 内部内部8MHz的阻容振荡器

- 用于CPU时钟的锁相环

ADC

- 12bit,8ch,1Msps

DMA

- 6路DMA 控制器

- 外设: UARTs, SPIs

GPIO

- 53 I/Os (16 IO x 3ea, 5 IO x 1ea)

调试方式

- 串行调试 (SWD)

定时器/PWM

- 看门狗*1 (32位减法计数器)

- 计时器*4 (32位或16位减法计数器)

- PWM*8 (带有6位可编程预分频器的32计数器/定时器)

通讯接口

- 3 UART (2个带有FIFO及流控的 UART, 1 个单UART)

- 2 SPI

- 2 I2C (主/从, Fast-mode (400 kbps))

加密

- 1 RNG (随机数生成器): 32位随机码

- 封装 : 64 TQFP (7×7 mm)

方框图

Documents

Data Sheet

Files

Reference Manual

Files

PHY Reference

Files

Errata Sheet

Files

W7500 Reference Schematics

IC+ PHY

W7500 Reference Schematic with IP101GA

W7500 Reference Schematic with IP101GRI

Realtek PHY

W7500 Reference Schematic with RTL8201CP-VD-LF

W7500 Reference Schematic with RTL8201F-VB-CG